# Algorithm Engineering

Peter Sanders

June 17, 2024

# **Contents**

| I | Met  | hodology                                         |    |   | 18        |

|---|------|--------------------------------------------------|----|---|-----------|

| 1 | The  | AE Cycle                                         |    |   | 19        |

|   | 1.1  | Modeling                                         |    | N | 23        |

|   | 1.2  | Design                                           |    |   | 23        |

|   | 1.3  | Analysis                                         | h. |   | 24        |

|   | 1.4  | Implementation                                   |    |   | 25        |

|   | 1.5  | Experiments                                      |    |   | 26        |

|   | 1.6  | Algorithm Libraries                              |    |   | 27        |

|   | 1.7  | Benchmarks and Competitions                      |    |   | 28        |

|   | 1.8  | Application Engineering                          |    |   | 30        |

|   | 1.9  | The History of AE                                |    |   | 31        |

|   | 1.10 | More Literature on AE                            |    |   | 32        |

|   |      |                                                  |    |   |           |

| 2 | Mac  | hine Models (with Darren Strash)                 |    |   | <b>34</b> |

|   | 2.1  | Turing Machines                                  |    |   | 37        |

|   | 2.2  | The von Neumann Model and its Variants           |    |   | 38        |

|   |      | 2.2.1 Random Access Machines (RAMs)              |    |   | 38        |

|   |      | 2.2.2 Register Machines                          |    |   | 40        |

|   |      | 2.2.3 The Real RAM                               |    |   | 40        |

|   |      | 2.2.4 Pointer Machines and Other Restricted RAMs |    |   | 40        |

|   |      | 2.2.5 Instruction Parallelism                    |    |   | 40        |

|   | 2.3  | External Memory                                  |    |   | 43        |

|   |      | 2.3.1 Sorting and Scanning                       |    |   | 44        |

|   |      | 2.3,2 What is the Block Size?                    |    |   | 45        |

|   |      | 2.3.3 Modeling Mechanical Hard Disks             |    |   | 46        |

|   |      | 2.3.4 Parallel Disks                             |    |   | 48        |

|   |      | 2.3.5 Solid-State Disks                          |    |   | 49        |

CONTENTS 3

|      | 2.3.6   | Other Nonvolatile Memory                              | 50 |

|------|---------|-------------------------------------------------------|----|

|      | 2.3.7   | Hardware Caches                                       | 51 |

|      | 2.3.8   | Cache-Oblivious Algorithms / Multilevel Hierarchies   | 52 |

|      | 2.3.9   | Virtual Memory                                        | 53 |

| 2.4  | Shared- | -Memory Parallel Models                               | 55 |

|      | 2.4.1   | Classical Parallel Random Access Machine (PRAM)       | 55 |

|      | 2.4.2   | Asynchronous PRAM                                     | 58 |

|      | 2.4.3   | Atomic Operations                                     | 59 |

|      | 2.4.4   | Lock-Free and Wait-Free Algorithms                    | 60 |

|      | 2.4.5   | The Work-Span Model                                   | 61 |

|      | 2.4.6   |                                                       | 62 |

|      | 2.4.7   | Graphics Processing Units (GPUs), Accelerators, etc   | 64 |

| 2.5  | Distrib | uted Models                                           | 68 |

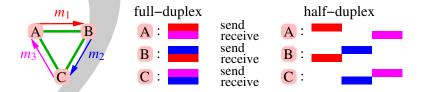

|      | 2.5.1   | Point-to-Point Fully-Connected Communication          | 70 |

|      | 2.5.2   | Communication-Efficient Algorithms                    | 73 |

|      | 2.5.3   | Bulk Synchronous Parallel (BSP, BSP*, BSP+, CGM) Mod- |    |

|      |         | els                                                   | 74 |

|      | 2.5.4   | Networks with Known Structure                         | 78 |

|      | 2.5.5   | Hierarchical Networks and Comb. with Shared Memory .  | 88 |

|      | 2.5.6   | Arbitrary Networks                                    | 89 |

|      | 2.5.7   | Cellular Automata                                     | 90 |

|      | 2.5.8   | Communication Complexity                              | 92 |

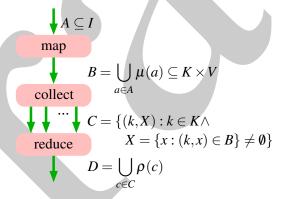

| 2.6  | MapRe   | educe and Other High-Level Models                     | 93 |

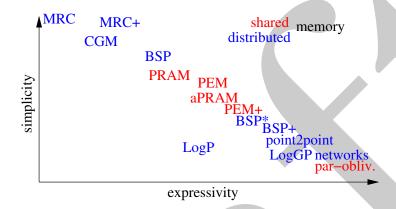

| 2.7  | Taming  | the Zoo of Parallel Models                            | 97 |

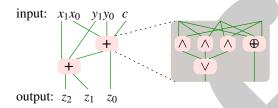

| 2.8  | Circuit | <b>s</b>                                              | 00 |

|      | 2.8.1   | Logical Circuits                                      | 00 |

|      | 2.8.2   | Physically Realistic Circuits                         | 02 |

| 2.9  | Stream  | ing Algorithms                                        | 04 |

| 2.10 | Fault T | olerance                                              | 06 |

| 2.11 | Private | Computations                                          | 10 |

| 2.12 | Quantu  | m Computing                                           | 11 |

|      | 2.12.1  | From Quantum Circuits to QRAMs                        | 12 |

|      | 2.12.2  | Quantum Annealing                                     | 14 |

| 2.13 | Further | Unconventional Models                                 | 17 |

|      | 2.13.1  | The Zoo of Turing-Complete Models                     | 17 |

|      | 2.13.2  | DNA Computing and Molecular Computing                 | 18 |

|      | 2.13.3  | Analog Computing                                      | 19 |

4 CONTENTS

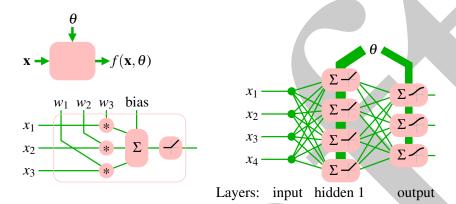

|   |      | 2.13.4 Neural Networks                             |  | 121 |

|---|------|----------------------------------------------------|--|-----|

|   | 2.14 | Energy Consumption and Other Resources             |  | 123 |

|   |      | 2.14.1 Energy Consumption in Current Architectures |  | 124 |

|   |      | 2.14.2 Energy Consumption in Future Architectures  |  |     |

|   | 2.15 | Summary and Outlook                                |  |     |

|   |      |                                                    |  |     |

| 3 | Prob | olem Models                                        |  | 129 |

| 4 | Algo | orithm Design                                      |  | 130 |

|   | 4.1  | Maintaining Loop Invariants                        |  | 130 |

|   | 4.2  | Case Distinctions                                  |  |     |

|   | 4.3  | Algorithm Schemas                                  |  |     |

|   | 4.4  | Greedy                                             |  |     |

|   | 4.5  | Divide-and-Conquer                                 |  | 131 |

|   | 4.6  | Multilevel Algorithms                              |  |     |

|   | 4.7  | Preprocessing and Kernelization                    |  |     |

|   | 4.8  | Randomization                                      |  | 131 |

|   | 4.9  | Using Data Structures                              |  | 131 |

|   | 4.10 | Make the Common Case Fast                          |  | 131 |

|   | 4.11 | (De)amortization                                   |  | 131 |

|   | 4.12 | Algebraic Techniques                               |  | 131 |

|   | 4.13 | Systematic Enumeration                             |  | 131 |

|   |      | Tabulation                                         |  |     |

|   |      | Dynamic Programming                                |  |     |

|   | 4.16 | Reduction                                          |  | 133 |

|   | 4.17 | Black-Box-Solvers                                  |  | 134 |

|   |      | 4.17.1 (Mixed( Integer)) Linear Programming        |  | 134 |

|   |      | 4.17.2 SAT and Consorts                            |  |     |

|   |      | 4.17.3 More Black-Box Solvers                      |  | 134 |

|   | 4.18 | LP-Type Problems                                   |  | 135 |

|   | 4.19 | Local Search                                       |  | 135 |

|   | 4.20 | Evolutionary Algorithms                            |  | 135 |

|   | 4.21 | More Bio (and Physics) Inspired Algorithms         |  | 135 |

|   | 4.22 | Portfolios                                         |  | 135 |

|   | 4.23 | Sweepline Algorithms                               |  | 135 |

|   | 4.24 | Reduction to Other Problems                        |  | 135 |

|   | 4.25 | Parallelization Techniques                         |  | 135 |

# Chapter 2

# **Machine Models**

# with Darren Strash

In Section 1.1, we introduced machine models as a necessity to abstractly design and analyse algorithms without reference to a particular hardware used to exe-

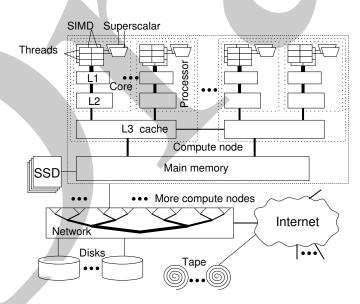

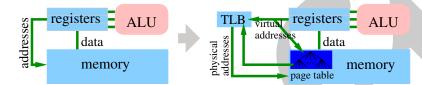

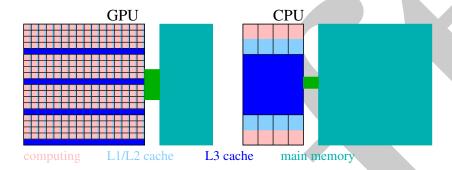

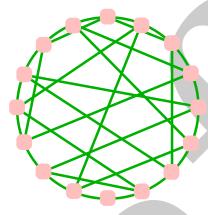

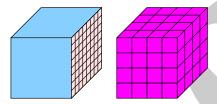

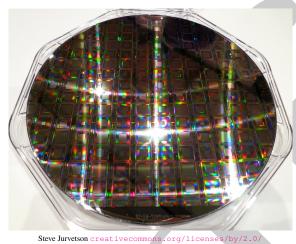

Figure 2.1: Some aspects of computer architecture for which we would like machine models.

cute a program. Generally speaking, we are facing a chicken-egg problem here. We can use machine models to abstract from existing hardware. But we can also strive to develop hardware that matches a certain model in order to simplify programming. The first view is usually justified since computer architecture often follows a quantitative approach [230] changing architectures to improve performance for existing benchmark programs. When this process comes up with new architectural features like caches or pipelines, models have to catch up to make it possible to develop new programs with reasonably predictable performance. This also helps in tuning existing programs.

But also the second view makes sense and can be observed in practice. For example, shared-memory multiprocessors with approximately symmetric memory access costs (SMPs) have been very successful and kept reappearing although complex memory hierarchies promise more peak performance; see also Section 2.5.5.

The "daily work" of an algorithm engineer faces a different question. Out of several or many available machine models, which one makes sense for the problem at hand? A straight-forward answer is to look at the machine one plans to use and pick the "standard" model used for it. A closer inspection shows that the Algorithm Engineering (AE) cycle of Chapter 1 is at work again. During design, analysis, implementation, or experimental evaluation, we may learn that we have to change the machine used or that we have to choose a different (perhaps more detailed) model to explain the peculiarities of the studied software. Switching the model may then also have a profound effect on the way we design and implement our software.

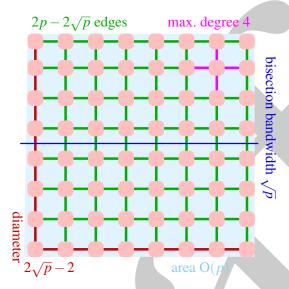

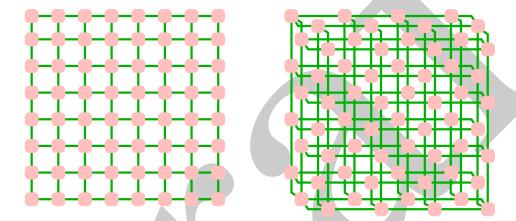

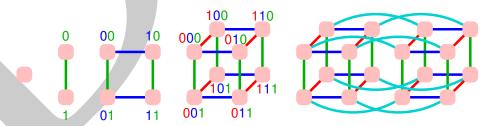

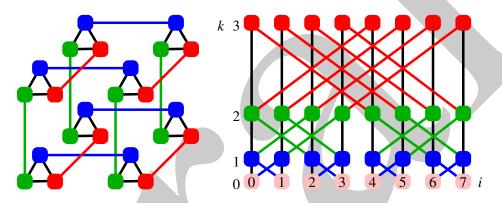

As already discussed in Section 1.1, modeling machines faces a difficult tradeoff between simplicity and fidelity. Figure 2.1 summarizes some aspects of computer architecture that one would like to model. In reality, things are even more complicated – aspects like instruction pipelining, branch prediction, virtual memory, transactional memory, memory access contention, or further complexities of different microarchitectures are not shown at all. To program a modern microprocessor, one has access to thousands of pages of documentation but there is no specification of how expensive a machine instruction is – indeed this varies with the concrete processor model and a lot of context (cache content, state of the execution pipeline, activities of other threads, temperature, etc.).<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>It is worth noting though that this complexity is a relatively new development. In his pioneering algorithmics book [277] Knuth specifies his MIX machine language where each machine instruction takes the same amount of time. In this model, the running time of a deterministic algorithm was a function that could in principle be analyzed analytically. One author's first computer

One way out is to work with one or several simple models that each consider one important aspect. The result can then be used to compare how well different algorithms take these aspects into account.

Open Problem 1 (Model-based auto tuning) The case for simplicity in machine models is closely connected to the readability of the result of an algorithm analysis. However, more complicated models can be used to produce complicated but accurate descriptions of the complexity of an algorithm. These can then help to derive the value of tuning parameters. While we know of several failed attempts at that, there are also success stories (e.g. [117]). Nevertheless, the approach seems to warrant additional research. The basic idea is to perform a detailed analysis of one or several algorithms/implementations that estimates their execution times as a function of parameters that describe the machine, input, and the configuration of the algorithm (tuning parameters). If the input and machine parameters are known (derived by measuring them or by requiring them as part of the input), one can use these formulae to select the best algorithm together with optimal tuning parameters. This is potentially much more powerful than traditional auto-tuning (e.g., [21, 42]) that blindly tries many combinations of tuning parameters for a fixed set of inputs in the hope that this finds good values that also work well for future inputs.

In the remainder of this chapter, we describe a wide spectrum of (more or less) simple models. In some cases, we add new variants that address limitations of the basic models. These variants all have a '+'-superscript added to their basic name. Often, we also explain complications of actual hardware going beyond these models. This can be helpful in performance tuning beyond theoretical analysis or in understanding deviations between analysis and experiments. However, the level of detail varies significantly. In part due to space constraint, the expertise (or lack thereof) of the authors, or perceived relevance to AE. For example, Section 2.3 gives a lot of detail on memory hierarchies where the author (and the AE community in general) have a lot of experience. On the other hand, our account of analog computing (Section 2.13.3) remains on a much more cursory level since it

<sup>(1983)</sup> used an INMOS 6510 processor which understood less than 100 simple machine instructions. Each instruction was documented in detail including the number of clock cycles needed to execute it. Hence, Knuth's approach still worked. Even in the late 1980s, processors like the Motorola 68000 were simple enough for this approach. Then, things like caching and pipelined instruction execution made processors faster but also less predictable. Research in real-time systems since then has struggled to be able to at least guarantee some upper bounds [481].

can currently be considered an exotic topic with more importance in the past but considerable potential for the future.

There is no crystal clear delineation between abstract machine models as discussed in this chapter and performance tuning for particular architectures. However, issues discussed in this modeling section have the property that one can describe the aspect to be optimized using a simple abstraction. For example, branch-prediction mechanisms are quite complicated but simply striving to avoid mispredictions is a good abstraction; see Section 2.2.5.

**Chapter overview.** In the following sections, we introduce concrete machine models. Sections 2.1–2.3 discuss increasingly refined models of *sequential* computing. Then Sections 2.4–2.7 present a large number of models for *parallel* computing, where Section 2.4 motivates its importance and where Section 2.7 attempts to bring some order into the "zoo" of possibilities. Section 2.8 on *circuits* takes a lower-level view on computing that allows us to reason about hardware. Sections 2.9–2.11 look at aspects of computing orthogonal to the descriptions above: processing data *streams* (Section 2.9) that do not fit into memory, *fault tolerance* (Section 2.10), and *privacy* (Section 2.11)

Section 2.12 deviates from classical models of computation by outlining some models for *quantum computing* which may revolutionize some areas of computing in the (near?) future. Indeed, there is no scarcity of further *unconventional* models, some of which are briefly discussed in Section 2.13 (e.g., DNA, analog, or neural computing).

While running time is the driving motivation between most of the models above, other resources like space, I/O volume or communication cost are also important. In particular, *energy consumption* is at least equally fundamental. Section 2.14 discusses how to take these resources into account. Section 2.15 summarizes the chapter with a brief look into conceivable futures.

# 2.1 Turing Machines

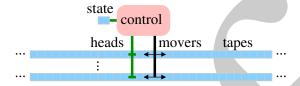

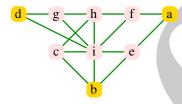

Perhaps the first abstract machine model was introduced by Alan Turing in 1936 [459] in order to characterize computability. A finite state machine operates on a tape by reading and writing symbols from a finite alphabet and by moving the tape. Allowing multiple tapes already gives surprisingly high flexibility in programming. See Figure 2.2 for an illustration. Turing machines are used in complexity theory and computability theory because of their great simplicity and flexibility. They are also useful to nail down the complexity of an algorithm in terms of bit

Figure 2.2: Multitape Turing machines.

operations, e.g., for integer multiplication [195, 226]. Turing machines seem less useful for designing algorithms that work well on real-world machines because they differ from them in important aspects (no random memory access, finite alphabet, etc.). However, there are notable exceptions; in their book [426], Schönhage et al. demonstrate how multitape Turing machines can be a good model for engineering numerical algorithms, such as dividing complex numbers or taking square roots.

Exercise 1 Describe a Turing machine model operating on a two-dimensional tape.

### 2.2 The von Neumann Model and its Variants

Most algorithm development, in particular in algorithm theory, is still done using the *von Neumann model* or one of its variants as described below. It goes back to one of the first designs for a universal digital computer [353] and it is a successful way to formalize the basic computational cost of an algorithm. However further aspects, such as memory hierarchies and parallelism, have to be considered later in order to arrive at really high performance in practice. In our experience, this is often more important than using advanced techniques in a simple model, such as complicated bit parallel operations.

### 2.2.1 Random Access Machines (RAMs)

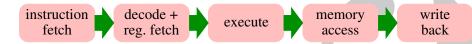

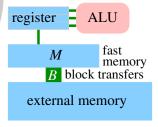

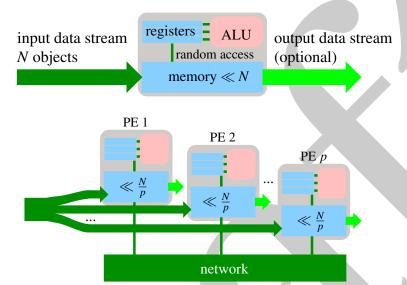

The random access machine (RAM) [431], in its modern form (the word RAM), has a computing unit, a register file, and a freely-addressable memory consisting of machine words.<sup>2</sup> See Figure 2.3. All operations execute in constant time.

<sup>&</sup>lt;sup>2</sup>There are several quite different definitions of the RAM model around. Often, RAMs are also confused with register machines; see Section 2.2.2. In particular, note that RAMs that are only

Figure 2.3: The RAM / von Neumann model. ALU stands for arithmetical logical unit.

Operations consist of load and store (also using indirect addressing), arithmetic operations on register operands, and (conditional) branches.<sup>3</sup> The textbook [412, Section 2.2] introduces a variant of this model in more detail – with all operations and an explanation of how pseudocode can be compiled into RAM operations so that we can directly do asymptotic algorithm analysis on pseudocode. The main point here is that by ignoring constant factors throughout, we can sweep many aspects of an actual microarchitecture under the rug. We will also assume an operation for generating machine words consisting of random bits. In reality, randomness is often "simulated" using pseudo-random number generators.

An important technical detail is the machine word size w. By default, it is  $\Theta(\log n)$ , where n is the input size. In particular, this allows a considerable amount of word-parallelism. It may seem odd that we can do a nonconstant amount of work in constant time. However, the alternatives are even odder. Constant-size machine words would not even allow us to address the input. This is the reason why Turing machine models are often used to discuss algorithms where bit-parallelism is not allowed. Sections 2.2.2 and 2.2.3 discuss the effect of unlimited word sizes.

**Exercise 2** Outline how to implement the set operations  $\cup$ ,  $\cap$ ,  $\neg$ , and  $|\cdot|$  for subsets of 0..n-1 in time O(n/w).

allowed to increment or decrement, despite being universal machines, are not useful for analyzing the complexity of algorithms.

<sup>&</sup>lt;sup>3</sup>From a mathematical point of view, we would get a slightly simpler variant of the RAM model by eliminating the register file. We choose to stick to it for several reasons: First, load-store architectures represent an important development in computer architecture (also part of the RISC versus CISC debate). In particular, access to registers is much cheaper than memory access in practice so we already get a first hint at memory hierarchies. On the theoretical side, dropping the memory gives us register machines as a special case.

## 2.2.2 Register Machines

On a RAM with unlimited word size, we can escalate word parallelism to such extremes that nondeterminism can be simulated with only polynomial-time overhead, giving P = PSPACE [225]. Nevertheless, this variant is useful to discuss computability in general. As a result, we no longer need memory; removing the memory from the RAM model gives the *register machine model*. Registers with "infinite" capacity are also implicit in the real RAM model discussed below.

#### 2.2.3 The Real RAM

In computational geometry [379, 131] one also considers the *real RAM* model where memory cells and registers can store real-valued numbers. Some operations are forbidden in this model (specifically the floor operation), otherwise the model is too powerful, similar to the register machine model. The real RAM is highly unrealistic yet allows us to abstract away issues related to numerical precision in order to develop the algorithmic basis of geometric algorithms. These can then be made realistic by using software libraries that support exact predicates on symbolic representations of real numbers [163]. For example, the real numbers most frequently needed in computational geometry can be represented as roots of a polynomial with rational coefficients (known as *algebraic numbers*). Other than exact computation, robust geometric computation can also be done with fixed precision, or by transformations that preserve a chosen topological property (such as planarity) [430].

## 2.2.4 Pointer Machines and Other Restricted RAMs

The full generality of the RAM model makes it difficult to prove lower bounds. Therefore, one also considers restricted variants. For example, *pointer machines* [425, 219] are models where arithmetic is not possible. Instead, a finite state machine operates on a dynamic graph. Other, more ad hoc restrictions are used for particular families of problems. For example, for sorting and related problems, we can consider elements that can only be moved, copied, and compared with a  $\leq$  operation but not otherwise manipulated or inspected.

#### 2.2.5 Instruction Parallelism

As a first small step to modeling parallel processing, one can take into account that modern microprocessors can execute several machine instructions in each clock

Figure 2.4: A simple 5-stage pipeline [230] that splits an instruction execution into fetching the instruction, decoding it and fetching input data that is stored in registers, performing actual calculations, memory access, and writing back results to registers.

cycle. This is achieved by *pipelining* and *instruction parallelism*. In pipelining, instruction execution is split into suboperations. Figure 2.4 shows a simple 5-stage pipeline. Current pipelines for high-performance processors are considerably longer – sometimes using 20 or more stages. There is one pipeline stage for each suboperation. Each pipeline stage handles one operation in each clock cycle. Several such pipelines are running in parallel – often specialized to particular types of operations (integer, floating point, load, store, etc.). Thus, overall, several dozen machine instructions are being executed in parallel at any point in time. This works fine for straight-line sequences of instructions without too many data dependencies between the operations. In this situation, conditional branch instructions are a problem because a branch can interrupt the stream of instructions. When this happens, many partially executed instructions have to be abandoned, their effect has to be rolled back, and it will take several clock cycles until the next instruction is completed.

Processors therefore invest considerable resources into *predicting* the outcome of a branch instruction. The instruction stream can then be continued in the predicted way without emptying the pipelines. In the most simple case, the compiler can predict a branch as taken or not taken. For example, the branch at the end of a repeat—until loop can be predicted as taken. This will fail only at the last iteration of that loop. More sophisticated techniques discover patterns in the most recent executions of a branch instruction using simple state machines [230]. Branch prediction works surprisingly well in practice. Computer architecture textbooks report typical rates of at least 90% correct branch predictions [230].

However, in some algorithms, branch mispredictions are hard to avoid. For example, efficient comparison-based sorting algorithms need about  $n \log n$  element comparisons. Traditional implementations of these algorithms associate one conditional branch with each of the comparisons. For fundamental information-theoretic reasons, these branches cannot be predicted at all – they are taken 50% of the time in a completely unpredictable way regardless of how much prediction

hardware is used. In such algorithms, the pipeline interruptions due to branch mispredictions can completely ruin performance. Algorithm analysis therefore sometimes also analyzes how many branch mispredictions can happen [352, 480]. More importantly, there are techniques to avoid conditional branches [264, 422, 159, 37]. This can greatly improve performance. In order to perform comparison-based algorithms without conditional branches, one has to dissociate comparisons from branches. The idea is that only very simple operations should depend on the comparison. For example, superscalar sample sort [422, 37] only performs an increment operation if a comparison operation computes the value **true**. Such simple operations can be done using *predicated instructions*. These are only executed if a special condition flag is set that is the outcome of a comparison. Otherwise, predicated instructions do nothing. Note that skipping one machine instruction costs only a fraction of a clock cycle while a branch misprediction costs several clock cycles.

\*Exercise 3 Develop a routine for binary search of an element x in a sorted array a of size n that uses conditional branches only for testing loop exit and for a conditional move of the form if c then a := b. You can assume that n is known at compile time. Discuss how to generalize the code so that it can make a batch of several searches in an instruction parallel way. Why is that still likely to be slower than searches based on implicit search trees as used in super scalar sample sort[422, 38]? Implement your solution and benchmark it compared to a more classical formulation of binary search, e.g., [412, Section 2.7].

**Open Problem 2** (**Priority queues without branch mispredictions**) Design a priority queue that avoids conditional branches like the super scalar sample sort [422, 37] and, at the same time, is as cache efficient as sequence heaps [398]. Can this be implemented in such a way that significant performance improvements are possible?

**Open Problem 3 (Where do branch mispredictions matter?)** Most algorithms where branch mispredictions are known to matter are comparison-based algorithms for sorting and related problems (e.g., merging and partitioning). Can you find further algorithmic problems? Flow computations? Monte Carlo simulations? How should these algorithms be modified to eliminate hard-to-predict branches?

**SIMD Instructions.** Another dimension of instruction parallelism is exploited

by *SIMD instructions* (aka *vector instructions*) that work on extra-wide registers (currently up to 512 bits) containing short vectors of numbers (e.g., 32 entries of 16 bits each). For example, an addition of two SIMD registers would add the two stored vectors component-wise.

# 2.3 External Memory

In computer architecture, there is a large spectrum of technologies for storing data. In particular, we face a tradeoff between price per bit on the one hand and speed on the other hand. Furthermore, there are fundamental physical reasons (like the limited speed of light) why a large memory must have large access latencies. Thus, there are good reasons why real-world (sequential<sup>4</sup>) computers with good performance must have both large cheap memory and small fast memory. This runs counter to the uniform memory in RAMs and a main principle in von Neumann's original idea of a universal computer [353]. We now discuss simple abstract models that grasp the resulting *memory hierarchy*.

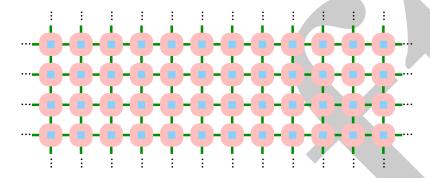

The basic *external* or *secondary memory* model (EM) [469], also called the I/O model, is very simple; see Figure 2.5. We have a random access machine with (fast) memory limited to M machine words. In addition, there is a large secondary memory. Access to secondary memory is in blocks of size B. In algorithm theory, analyzing external memory algorithms amounts to counting the number c of block accesses (I/Os). Sometimes we also use the I/O volume is then cB. In AE, we additionally analyze the *internal work*, e.g., by counting executed machine instructions as in the RAM model. The simplicity of the EM model makes it very

<sup>&</sup>lt;sup>4</sup>For parallel architectures, there is an option to partition a large cheap memory into many small pieces, each equipped with its own processor core that then has small uniform access latency to its *local* piece of memory (aka *processing in memory* (PIM) [265]); see also Sections 2.4.6 and 2.5.5.

Figure 2.5: The external memory model

flexible. Slow and fast memory can be any two levels of the physical memory hierarchy. The two levels hard disk and main memory were originally most important. Today, main memory and some unspecified level of the cache hierarchy are at least equally important. The EM model is highly successful because of its simplicity and because algorithms that perform well in this model often also perform well in practice; see [331, 468] for overviews of results.

In the subsequent sections, we present further details and variants of the EM model. This is perhaps the most detailed elaboration of a family of models in this book. We view this as a convenient example of how a simple successful model can relate to reality and refined models. The reader should assume that many of the remaining models in this book deserve a similar amount of further detail. Section 2.3.1 explains how many EM algorithms or their complexity can be expressed based on sorting and scanning primitives. Sections 2.3.2 and 2.3.3 discuss how the EM model does (or does not) grasp details of a real-world machine. Then Section 2.3.4 generalizes the EM model to handle parallel disks. These are the basis for modeling solid state disks in Section 2.3.5 and other nonvolatile memory in Section 2.3.6. Peculiarities of hardware caches are discussed in Section 2.3.7. Section 2.3.8 then explains how a simple twist of the EM model can be used to model algorithms that perform well in multilevel memory hierarchies. Finally, Section 2.3.9 discusses how virtual memory affects algorithm analysis and design. Another variant of the EM model yields a useful model for parallel memory hierarchies; see Section 2.4.6.

# 2.3.1 Sorting and Scanning

Two simple algorithmic techniques permeate the design of external memory algorithms:  $Scanning\ n$  elements (machine words) is possible with n/B I/Os. The shorthand scan(n) is used for this expression.  $Sorting\ n$  elements takes  $sort(n) = \Theta(n/B\lceil 1 + \log_{M/B} n/M \rceil)$  I/Os [6]. Using multiway mergesort (Section 11.1.3) we can see that an upper bound for the constant factor in sort(n) is 2 for sorting machine-word-sized elements.

**Open Problem 4** (Exact lower bound for external sorting) The constant factor in the lower bound is still open. Aggarwal and Vitter [6] basically show a factor of 1 and that the factor becomes 2 when one assumes that the number of inputs is the same as the number of outputs. However, this leaves open the existence of more efficient algorithms that do an asymmetric amount of reading and writing.

**Exercise 4** Describe an external sorting algorithm that needs just  $\lceil n/B \rceil$  output operations. You can expend a large number of input operations. But try to limit them to  $O(n^2/BM)$ . Also, limit internal work to  $O(n^2 \log n/BM)$ .

The sorting bound is also a lower and/or upper bound for many other computational problems even if the actual algorithms used to solve them are quite different.

From an AE perspective, sorting and scanning are convenient ways to distinguish more or less complicated algorithms in a qualitative sense. However, in practice, the term  $\lceil \log_{M/B} n/M \rceil$  is exactly one<sup>5</sup> in many situations. Let us consider the case of hard disk versus main memory. In the last few decades, the cost ratio between mechanical hard disk memory and RAM has remained at around 200. This ratio is not likely to increase dramatically as long as RAM capacities improve at least as fast as hard disk capacities. Hence, in a *balanced* system with similar investments for both levels of memory, the ratio between input size and internal memory size is not huge. In particular, M/B is likely to be much larger than than the cost ratio. But as long as M/B > n/M, we have  $\lceil \log_{M/B} n/M \rceil = 1$ . The cost ratio for nonvolatile memory<sup>6</sup> (SSDs) versus main memory is even smaller. We can have  $\lceil \log_{M/B} n/M \rceil > 1$  when straddling several layers of the memory hierarchy, e.g., when fast memory is L1 cache size (kilobytes) and slow memory is the main memory of a large server (terabytes).

#### 2.3.2 What is the Block Size?

On the first glance, the block size B is a parameter defined by the hardware, e.g., the cache line size of a certain hardware cache level. However, a closer look reveals that often there is not one clear block size imposed by the hardware and that B should actually be considered a tuning parameter of the implementation.

This is particularly clear for mechanical hard disks. There are hardware-imposed block sizes used for error detection and correction. However, these values are much too small to be useful for external memory algorithms. A reasonable *linear model* for the time to access  $\ell$  consecutive bytes of data on a hard disk is  $\alpha + \beta \ell$  where  $\alpha$  is a startup overhead accounting for mechanical and software delays and where  $\beta$  is the achievable data rate once access has started. Indeed, it might be attributed to a historical accident that this model is unusual for hard

<sup>&</sup>lt;sup>5</sup>Of course, the value is zero when processing can be done within internal memory.

<sup>&</sup>lt;sup>6</sup>Nonvolatile memory does not lose its state when the power is switched off.

disks but standard for message passing; see Section 2.5. The above linear model suggests that  $B \approx \alpha/\beta$  is a reasonable value for the block size. If we make random accesses that actually need less data per access, we are at most twice as slow as using a small block size. If we make a large consecutive access we are at most twice as fast as accessing the same amount of data with random access of block size  $\alpha/\beta$ . For current hard disks, this means that block sizes should be a couple of megabytes. However, we can also turn this argument around. We can achieve acceleration up to a factor of two by choosing a block size more appropriate for the application at hand. For example, for sorting we can choose large block sizes as long as this leaves  $\lceil \log_{M/B} n/M \rceil$  at a value of 1. For index data structures with access time  $O(\log_B n)$ , we may want to choose smaller blocks; see also Section 13.2.

We have moved this discussion outside the section on hard disks because it emphasizes the fact that block sizes are tuning parameters. At the other extreme, even hardware cache lines may not be the right choice for the tuning parameter *B*. For example, many Intel processors access two consecutive cache lines considerably faster than two arbitrary cache lines. Hence, setting *B* to two (or more) cache lines may be a reasonable choice.

## 2.3.3 Modeling Mechanical Hard Disks

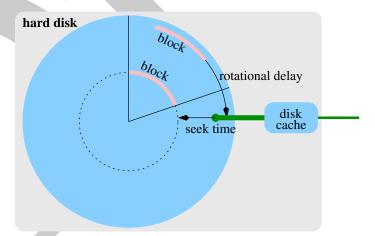

In Section 2.3.2 we used the formula  $\alpha + \beta \ell$  for modeling the time needed to access  $\ell$  bytes of data on a disk.<sup>7</sup> This is a gross oversimplification for mechanical hard disks. There are three main additional issues illustrated in Figure 2.6.

- A. The disk *rotates* and the time needed to rotate to the beginning of the intended data block depends on the current rotation angle. Thus, for a particular data block, the *rotational delay* will oscillate over time corresponding to a sawtooth-shaped periodic function.

- B. The access head has to *seek* to the right track before accessing a block.

- C. The disk rotates at fixed angular velocity<sup>8</sup> and the data is stored with an (approximately) fixed number of bits per millimeter of disk surface. This

<sup>&</sup>lt;sup>7</sup>Hard disks are getting less and less important as this book is written. We still believe that this section remains interesting as an example of how more detailed modeling can have an appreciable performance impact yet is also impractical in many cases.

<sup>&</sup>lt;sup>8</sup>There are exceptions, e.g., audio CDs.

implies that data stored on the outer zones of the disk is transferred faster than data on inside zones. Further complications arise for example due to caching within the disk and because faulty tracks on the disk are replaced by reserve tracks (usually on the slow inside zones of the disk).

These peculiarities can in principle be exploited for algorithm tuning. Batches of blocks to be read may be scheduled so that overall rotational delays are minimized [191, 445]. Data accessed together can be stored close together. Important data could be stored on outer zones.

Such tuning measures are good examples of optimizations one should often *avoid* since they can be fragile and nonportable. These optimizations should only be done on the right level of the software stack and using the right abstractions. The processor controlling the disk can try to perform optimizations for issues A and B when it is given batches or queues of outstanding I/Os. A disk usually presents itself to the operating system as an array of blocks. Hence, the operating system or a runtime system of a database could perform optimization for issue C if it is understood that blocks with the smallest index are the fastest ones.

Figure 2.6: Schematic drawing of a mechanical hard disk – illustrating seek time, rotational delay, and different data densities.

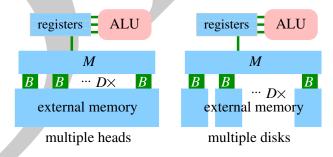

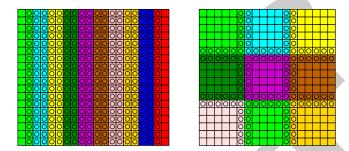

#### 2.3.4 Parallel Disks

The external memory model has been generalized to consider *D* identical disks – in one I/O step, *D* blocks can be transferred [6, 469]. Aggarwal and Vitter [6] propose a simple variant where *any D* blocks can be accessed (referred to as *access-any* variant). Vitter and Shriver [469] allow only *one* block to be accessed from *each* disk (access *one-each*). Figure 2.7 depicts these two model variants. In both variants, we can hope to reduce the number of I/O steps by a factor up to *D*. To achieve this speedup, we need enough parallelism in the application. The one-each variant in addition requires clever data allocation and disk scheduling (e.g., see [141, 251] for sorting).

The one-each variant is more realistic than the access-any variant. The access-any variant is still useful because it allows to discuss parallelism independently of memory allocation and scheduling – see also Section 2.3.5 on SSDs. Moreover, the access-any variant can emulate the one-each variant with surprisingly small overhead [409] (a small constant factor using randomization) and there are generalizations to asynchronous access, heterogeneous disks, etc. [399, 400].

**Exercise 5** Give an example access pattern, where the one-each variant of the parallel disk model takes D times more input steps than the access-any variant. What changes with this pattern if each data block is independently allocated to a random disk?

A simple way to exploit parallel disks is striping – we concatenate D physical blocks of size B to one logical block of size DB. We can then apply any single-disk algorithm using block size DB. This automatically exploits disk parallelism

Figure 2.7: The external memory model with parallel heads (access any) [6] and parallel disks (access one-each) [469].

in a perfectly load-balanced fashion. The problem with this approach is that not all applications can make very good use of such large block sizes or that there may not be enough fast memory to store enough blocks in internal memory.

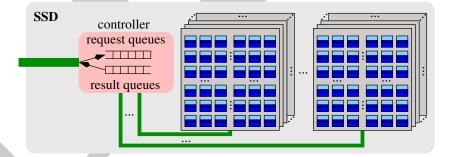

#### 2.3.5 Solid-State Disks

Solid-state disks (SSDs) are built using semiconductor technology that does not lose its memory when power is lost [332, 7]. Access is done in blocks to hide access latencies and to simplify error correction. SSDs are cheaper than RAM because their cells are slightly smaller, because they store several bits per cell, and because one can stack memory cells in hundreds of layers. On the other hand, SSD access is slower than RAM access. At the time of writing, SSDs are rapidly replacing mechanical hard disks in more and more applications – they are faster, more compact, and need less power. In particular, the nonvolatile memory of a smartphone is essentially an SSD.

SSDs have smaller blocks than hard disks, higher overall bandwidth, and much lower access latency. There are also two important qualitative differences compared with hard disks. First, there is a marked asymmetry between reading and writing. Writing is usually slower, consumes more energy, and often uses larger block sizes than reading. More precisely, what is most expensive and uses larger blocks is *erasing* data blocks which is required to overwrite them with different data later. Also, erasing the same physical block multiple times wears it out and eventually destroys it. The disk controller therefore employs *wear-leveling*

Figure 2.8: Schematic drawing of a solid state disk (SSD). Each cell stores several bits. Many layers of cells and chips side by side give significant parallelism in request processing.

algorithms that change the mapping from logical to physical blocks to spread out write accesses over the entire disk. For the user, it is important that background processes for wear-leveling and erasing invalidated blocks can cause performance anomalies in particular for applications with complicated writing patterns. Also, a nearly full SSD can be much slower for writing than an empty one.

The second important difference is that to achieve maximum throughput of random disk accesses, one needs to make many accesses in parallel. The currently dominating NVM Express protocol (NVMe) therefore offers 2<sup>16</sup> command FIFO queues, each of which can buffer up to 2<sup>16</sup> commands. Figure 2.10 illustrates this view of an SSD. For example, in an external hash table benchmark [282] we use an asynchronous parallel approach where up to 128 requests can be in flight at a time. In a sense, each SSD device behaves like an array of many small parallel disks. However, we have no control over the allocation of logical blocks to these "sub-disks".

Overall, two simple models for SSD seem reasonable. We can use the single-disk EM model with a block size much larger than the physical block size of the SSD. This will exploit the parallelism within the SSD because the controller internally stripes large blocks over the different memory modules. For applications with many random accesses to small data objects, it is better to use the access-any variant of the parallel disk model with a sufficiently large value of *D* to grasp the parallelism within the SSD. The more complex one-each model is not helpful here since we have no control over the allocation of blocks to disks.

**Exercise 6** Produce a table comparing mechanical hard disks, SSDs and DRAM memory at the current technology and market prices. Possibly include both mainstream and high-end variants of the hardware. Compare cost per bit, bandwidth, latency, and energy consumption. Document your methodology – from where do you get the prices? How do you define latency? For energy consumption, can you differentiate between reading, writing, and idling? For hardware that you actually have at hand, try to compare actual measurements with data sheets or benchmarks done elsewhere. Discuss differences.

#### 2.3.6 Other Nonvolatile Memory

SSDs may be only an intermediate step to nonvolatile memory that looks more like main memory than like a disk. This means that block sizes are cache line sizes and that reads are as fast as for main memory. Writes may still be more expensive in terms of time and energy consumption and the memory may wear out faster

so that the number of write operations to a cache line has to be limited. This situation can be analyzed in the context of write-efficient algorithms [74] where one considers write operations to main memory to be a factor  $\omega$  more expensive than read operations. Another interesting aspect of this is how to make algorithms persistent when using such memory, i.e., to allow restarts after failures that erase the local state of the processors and the content of the fast memory [76, 479].

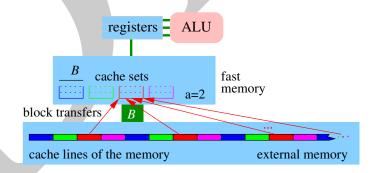

### 2.3.7 Hardware Caches

One assumption of the EM model is that the algorithm has full control over the content of the fast memory. In contrast, the content of a processor cache is controlled by the hardware. A typical strategy are *a-way set associative* caches [230], where a is a small constant: Suppose the cache contains ak cache lines. It is then divided into k cache sets of size a. Cache line i is mapped to cache set i mod k. Each cache set is managed separately using (an approximation of) the least recently used eviction strategy (LRU), i.e., when a new cache line enters a cache set s then the least recently used block in s is evicted; (see also Section 2.3.9). Sometimes the LRU strategy is only approximated. The case a = 1 is called direct-mapped cache. Figure 2.9 illustrates this variant of the EM model.

In practice, set-associative caches work quite well, even for relatively small values of a [230], e.g., a = 4. However, bad situations may arise. Even direct-mapped caches are efficient if one maintains full control over memory allocation and simple deterministic access patterns of the algorithm. For more complex access patterns there is less previous work. In [327] we consider the situation where the program scans k arrays of total length n. This covers many external memory

Figure 2.9: External memory with set-associative fast memory.

algorithms akin to sorting. If k > a, every element access may cause a cache fault in the worst case. However, if the starting addresses of the arrays are randomized, O(n/B) cache faults suffice provided that  $k = O(M/B^{1+1/a})$ . One can also bypass the hardware cache replacement [189, 429] – although at the cost of considerable overhead.

Exercise 7 For the computer you are mainly using, try to find as much information as you can on its memory hierarchy: how many cache levels? block sizes? associativity of each level? speed? Make a table and document your sources.

# 2.3.8 Cache-Oblivious Algorithms / Multilevel Hierarchies

Of course, we can design algorithms that explicitly handle multiple levels of memory hierarchy and then analyze the number of I/Os for each level. However, this is rarely done since it leads to complicated algorithms and complicated results of the analysis. Anyway, in practice usually two levels of the hierarchy will be the performance bottleneck so that setting the parameters B and M of the EM model to these parameters will yield an efficient program. However, which two levels are relevant may depend on the actual machine and on the size of the input. For example, when the input fits in the L3 cache, L2 cache misses may be the performance bottleneck whereas, for large inputs, L3 cache misses may dominate. Hence, in general we need an (auto)tuning mechanism to tune the parameters B and M.

An elegant alternative to tuning is to design I/O-efficient algorithms that do not rely on the values of B and M. Such *cache-oblivious algorithms* are automatically efficient for all levels of the memory hierarchy [189, 280, 25]. For example, an algorithm that just scans an array of size n will need  $\mathrm{scan}(n)$  I/Os regardless of the concrete values of B and M. Section 9.3 describes cache-oblivious unbounded arrays and queue-like data structures. Hashing with linear probing (Section 10.4.1) is another simple example for a cache-oblivious algorithm.

**Open Problem 5** (**AE for cache-oblivious algorithms**) Few cache-oblivious algorithms have been evaluated experimentally [89, 228, 91]. Even fewer can actually compete with the best cache-aware algorithms. Even defining "compete" is an interesting question here. How much overhead is worth the robustness of avoiding tuning? Does the cache-oblivious algorithm ever outperform a cache-aware algorithm that uses fixed values for M and B across all inputs and machines? Hence, AE for cache-oblivious algorithms is a wide-open topic.

**Exercise 8** Perform a case study on engineering algorithms for matrix transposition. Previous algorithms and proof-of-concept implementations [280, 189] can serve as a starting point. To simplify the situation, assume that we transpose  $2^k \times 2^k$ -matrices out-of-place, i.e., the result is in a separate piece of memory. Compare

- a) A straight-forward nested loop implementation

- b) A tuned cache-aware algorithm that cuts the matrix into tiles of size B × B. Subroutines for moving or swapping and transposing tiles should be carefully tuned.

- c) A simple recursive cache-oblivious algorithm

- d) A tuned cache-oblivious algorithm that uses a tuned base case and a tuned copy operation that may be similar to the ones developed for 2.

- e) A carefully tuned code from a numerical library.<sup>9</sup>

Compare the versions for different input sizes and on different architectures.

#### 2.3.9 Virtual Memory

Virtual memory is a combined hardware/operating system mechanism that allows all processes to use the same logical address space starting from 0. Ideally, this mechanism should be invisible. However, performance penalties due to the translation of virtual to physical addresses do show up and can also be modeled. One important effect is due to the *translation lookaside buffer (TLB)* – a cache for *m* page addresses that allows us to quickly translate accesses to these pages. TLB misses can be modeled like cache faults for a cache where page size *B* is the virtual memory page size and where the cache size is M = mB. One can reduce TLB misses by configuring the operating system to use larger page sizes. Applications that have many TLB misses (e.g. when they frequently access large hash tables) experience memory access delays that are not constant but grow with the input size. The reason is that tree-like data structures are used to resolve TLB misses [262].

<sup>&</sup>lt;sup>9</sup>The documentation of operation *cmatrixtranspose* in the Alglib library (www.alglib.net/translator/man/manual.cpp.html, accessed Oct. 17, 2023) mentions that it is actually using a cache-oblivious implementation. Often matrix transposition is a special case of a more flexible operation, e.g., with the suffix *matcopy*.

Figure 2.10: Left: schematic of the RAM model with the address data path exposed. Right: refined model of the address data path taking translation lookaside buffer (TLB) and the page table data structure into account.

Virtual memory also supports programming techniques that would otherwise not be available. For example, the Templated Portable I/O Environment (TPIE) library for external memory computing [27] uses operating system mechanisms to emulate a logical memory that is larger than the physical memory. However, most efficient implementations of external memory algorithms use more efficient and more flexible mechanisms. A related (efficient) technique is *memory over-committing* where the logical address space used is larger than the physical one but the program never accesses more than the physically available memory. This allows the allocation of several large arrays whose total size is known but whose individual size is unknown. Section 10.8 gives an application for space-efficient hash tables.

When a large external memory is used to extend a small physical memory, efficient caching mechanisms become essential. The LRU strategy mentioned in Section 2.3.7 is considered reasonably effective here. However, it is expensive to implement it precisely. Therefore, various approximations are considered whose precise implementation depends on the capabilities of the required hardware. For example, one can maintain a (possibly approximate) priority queue of cached pages whose priority is a time stamp. Since maintaining precise time stamps is too expensive, one can maintain a lower bound for the last access. When a page has the lowest-known bound, it is not immediately evicted but goes into a (possibly approximate) FIFO of eviction candidates. In addition, the page is marked to throw an exception when it is accessed next. If this happens before the page is actually evicted, a fresh timestamp is noted and used to reinsert it into the priority queue.

A disadvantage of LRU is that it caches data that is merely scanned and never accessed again. Therefore various refinements have been designed that evict pages that are "not in active use".

# 2.4 Shared-Memory Parallel Models

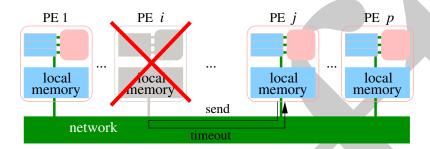

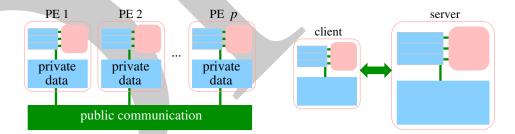

Perhaps the main weakness of the RAM model is that it considers only sequential algorithms. However, it is difficult to make sequential computers faster. Increasing the clock frequency reduces energy efficiency. Increasing instruction parallelism only helps for a limited set of computations. Increasing the size of the memory increases access latencies. Overall, there is a limited return on investment regarding performance when one invests more transistors or more energy to get faster sequential computers. These limitations can be overcome by looking at parallel computing that allows near-linear scaling of computing power with the invested resources. Not surprisingly, the most successful models of parallel computing are slight generalizations of the RAM model. In this section, we begin with the approach to keep a global *shared* memory and to replicate the processing cores. Section 2.5 replicates RAMs and connects them by a network. A more abstract view taken in Section 2.6 is to look at a small set of parallelizable operations applied to sets or sequences

We begin with the simple PRAM in Section 2.4.1 that can already serve as a basis for devising parallel algorithms in a high-level fashion, concentrating on exposing the parallelism in the problem. There, we also introduce several important conventions for analyzing parallel algorithms. On the other hand, real shared-memory machines are ubiquitous now from smartphones to servers with hundreds of cores. Further subsections cover important aspects of real-world shared-memory machines.

# 2.4.1 Classical Parallel Random Access Machine (PRAM)

A PRAM consists of p execution units (PEs) of random access machines (RAMs, Section 2.2.1) attached to a single shared memory. The PEs are numbered from 1 to p (or from 0 to p-1, or whatever is most convenient for the algorithm description), which are their IDs. As in the RAM model, instructions are assumed to need constant time. The PEs work in a lockstep fashion, i.e., those PEs that load a memory cell do so based on the value at the beginning of a time step. Those that write a value to a memory cell store this value during the step and the value is visible there in the next time step.

PRAMs come in several variants depending on the rules for concurrent access to the same memory cell. In the acronyms for these variants, an "E" stands for "exclusive", i.e., concurrent access to the same memory cell in the same time step is forbidden and a "C" stands for "concurrent", i.e., concurrent access is allowed.

Figure 2.11: The parallel random access machine (PRAM).

By distinguishing between read access (R) and write access (W), we get three main model variants – EREW, CREW, and CRCW.

**Exercise 9** What would an ERCW PRAM be? Discuss why this variant is not important.

For CRCW PRAMs there are several submodels depending on the semantics of concurrent writes:

**Common:** Concurrent accesses are only allowed if all PEs that attempt to write to the cell concurrently write the same value. This is the weakest model variant but is already surprisingly powerful.

**Arbitrary:** If several different values are written concurrently to a cell, one of these values will be stored. The algorithm has to remain correct regardless of which of the values is chosen.

**Priority:** Among the PEs that try to write, the one with the smallest PE ID writes. This should not be confused with a prioritization based on the written value which falls into the Combine category below.

**Combine:** A commutative and associative operation like sum, min, max, or xor is applied to the written values. This is a fairly expensive operation.

Table 2.1 gives examples.

An abstract representation of a PRAM computation is a directed acyclic graph (DAG) of elementary operations where one measures the size of the DAG (work) and the number of operations on its longest path (span) which is a measure for the *latency* of a computation. The goal is often to achieve work similar to the best-known sequential algorithm and low span, preferably polylogarithmic in the

| it variants of the ere with model. |                                     |              |                     |          |             |  |  |

|------------------------------------|-------------------------------------|--------------|---------------------|----------|-------------|--|--|

| ir                                 | ıput                                |              | result              |          |             |  |  |

| PE 1 P                             | E 2 PE 3                            | 3   Common   | Arbitrary           | Priority | Combine-Add |  |  |

| 3                                  | 3 3                                 | 3            | 3                   | 3        | 9           |  |  |

| 1                                  | 2 3                                 | Error        | $x \in \{1, 2, 3\}$ | 1        | 6           |  |  |

| 2                                  | 1 3                                 | Error        | $x \in \{1, 2, 3\}$ | 2        | 6           |  |  |

| edges go<br>downwards              | 2 5                                 | 1 7 8 5 9    | 9 5 2               | 5 1 7 3  | 8 5 9 5     |  |  |

|                                    | $\stackrel{1}{2}$ $\stackrel{1}{7}$ | 8 15 23 28 3 | 7 42                | 7 8 15 2 | 3 28 37 42  |  |  |

Table 2.1: Results of a concurrent write operation to memory cell 42 using different variants of the CRCW PRAM model.

Figure 2.12: DAGs for two ways to compute 8-element prefix sums. Left: with span and work 7 (additions). Right: with span 3 and work 12.

input size n, i.e.,  $\log^{O(1)} n$ . See Figure 2.12 for an example. Note the relation to the size and depth of a circuit explained in Section 2.8.1.

PRAMs have been criticized as unrealistic because of their lockstep operation principle and because they do not account well for communication costs. However, our impression is that this criticism is only partially warranted. PRAMs are an easy way to express parallelism and are thus a logical first step to a parallel algorithm. Many PRAM algorithms have later been implemented on realistic machines. In our opinion, what should be questioned is the large number of *inefficient* PRAM algorithms that invest a polynomial factor of additional work in order to achieve a polylogarithmic span. However, this issue is not so much due to problems with the PRAM model but with an unrealistic framework for algorithm analysis.

Open Problem 6 (Slow but efficient parallel algorithms) Polylogarithmic span has been a primary objective of parallel algorithm development since the 1980s for complexity-theoretic reasons [215] – problems that do not allow polylogarithmic span were deemed to be hard to parallelize. However, from an AE perspective, *efficient* algorithms with larger span, such as  $n^{\alpha}$  for  $\alpha < 1$ , are perfectly fine. Can we find such algorithms for problems that are otherwise hard, e.g., BFS, strongly

connected components (see also [179, 144])? Recently, several promising theoretical results in this direction have been achieved for problems related to graph reachability [257, 176].

Exercise 10 Describe fast algorithms that perform the logical and of n Boolean values using n PEs of a PRAM for a) CREW PRAM; and b) common CRCW PRAM. Compare the achieved running times.

## 2.4.2 Asynchronous PRAM

To refine PRAM algorithms for real-world shared-memory machines, one can use an asynchronous model with queued writing [202, 203, 412]. This is a clean model of the memory access *contention* that is a major performance problem in practice. Let us single out the aCRQW PRAM model – the asynchronous concurrent read queued write PRAM [412, Section 2.4.1]. We assume concurrent reads without delays since the local caches of the PEs enable contention-free concurrent read accesses in many practical situations. However, concurrent writing to the same memory cell involves *queuing*. More concretely, a FIFO queue is associated with every memory cell. During any clock cycle and for any cell C, first, all read operations to C return its old value. Then write operations to C are appended to the queue of C – possibly several ones. Finally, the first write operation in the queue of C is executed and the corresponding operation finishes. The remaining write operations remain in the queue, delaying the corresponding PEs. Table 2.2

Table 2.2: Example of queued writing where PEs 1–3 concurrently access memory cell *S*[42]. Each row corresponds to one clock cycle on an aCRQW PRAM (which is still an abstraction of a real-world machine).

| 3[42]                    |              |             |             |

|--------------------------|--------------|-------------|-------------|

| value queue              | PE 1         | PE 2        | PE 3        |

| $0$ $\langle\rangle$     | S[42] := 11  | S[42] := 22 | S[42] := 33 |

| 11 $\langle 2,3 \rangle$ | S[42] := 111 | queued      | queued      |

| $\langle 3,1 \rangle$    | queued       | instr. x    | queued      |

| 33 (1)                   | queued       | instr. y    | instr. v    |

| 111 $\langle \rangle$    | instr. u     | instr. z    | instr. w    |

<sup>&</sup>lt;sup>10</sup>In practice, contention may also happen when different cells are accessed, e.g., when they are located in the same cache line (*false sharing*). Careful implementation can often avoid such effects.

gives an example. Other operations may also vary in their execution time – we drop the lockstep synchronization assumed for PRAMs. Further variants can be considered.

## 2.4.3 Atomic Operations

To achieve consistent behavior in asynchronous shared-memory machines, we need atomic operations that perform a set of memory operations uninterrupted by other PEs; see also [412, Section 2.4.3]. The most widely considered atomic operation is compare-and-swap (CAS). A call CAS(i, e, d) specifies a value e expected to be present in memory cell i and the value d that it wants to write. If the expectation is true, d is written to memory cell i, the operation succeeds by returning 1. If the value is different, some other PE has modified cell i in the meantime. CAS writes the new value of cell i into e and fails by returning 0. See Table 2.3 for an example. CAS can be used to implement locks and other synchronization primitives. It can also be used to update the content of a cell. For example, a loop of CAS operations can be used to atomically add an offset to the content of a cell. This fetch-and-add operation as well as similar update operations are also directly supported by many architectures (see Table 2.4 for an example). Particularly special are priority updates, where [434]  $S[i] := \max(S[i], x)$ . If one assumes that updates arrive in an order that is not correlated to their value, the cell value changes only a logarithmic number of times and thus the updates lead to little contention.

Table 2.3: Example of two concurrent CAS instructions executed on memory cell S[42] in the aCRQW PRAM model. The columns labelled  $R_1$  and  $R_2$  give the current value of these registers. PE 1 succeeds in writing the value 1. PE 2 is first queued and then its CAS instruction fails because the actual value of S[42] is now 1 while value 0 was expected. The actual value is returned in register  $R_1$ .

| S[42] |                     | PE 1                     |       |       | PE 2                     |       |       |

|-------|---------------------|--------------------------|-------|-------|--------------------------|-------|-------|

| val   | queue               | instruction              | $R_1$ | $R_2$ | instruction              | $R_1$ | $R_2$ |

| 0     | $\langle \rangle$   | $R_2 := CAS(42, R_1, 1)$ | 0     | -1    | $R_2 := CAS(42, R_1, 2)$ | 0     | -1    |

| 1     | $\langle 2 \rangle$ | instr. x                 | 0     | 1     | queued                   | 0     | -1    |

| 1     | <b>〈</b> 〉          | instr. y                 | 0     | 1     | instr. z                 | 1     | 0     |

Some architectures support *transactional memory*. Here, a computer program can label a (small) subsequence of instructions as a *transaction*. The hardware

Table 2.4: Example of two concurrent fetch-and-add operations incrementing memory cell S[42] in the aCRQW PRAM model.

| <i>S</i> [42] | queue               | PE 1           | PE 2           |

|---------------|---------------------|----------------|----------------|

| 0             | $\langle \rangle$   | fetchAdd(42,1) | fetchAdd(42,1) |

| 1             | $\langle 2 \rangle$ | instr. x       | queued         |

| 2             | $\langle \rangle$   | instr. y       | instr. z       |

guarantees that a transaction is either executed atomically or fails without changing the memory. Transactions can immensely simplify the design of concurrent programs and they often improve performance. A downside is that there are no hard guarantees that transactions will eventually succeed (perhaps after some retries). Hence, a program also needs a fallback implementation using traditional techniques such as locks or simpler atomic operations.

**Exercise 11** Repeat Exercise 10 (logical and) for the aCRQW PRAM using CAS instructions. How can you achieve logarithmic worst-case execution time?

# 2.4.4 Lock-Free and Wait-Free Algorithms

Multiple threads can stand in each other's way in highly complicated ways. For example, three threads might wait for locks held by other threads in a cyclical fashion – a deadlock situation that can bring the system to a standstill. A particularly complex situation is when a thread t holds a lock  $\ell$  and then is itself blocked; for example, because it currently does not have a PE assigned to it by the operating system or because it waits for the completion of an I/O operation. Thread t can then delay many other threads waiting to acquire lock  $\ell$ . Therefore, there has been intensive work on algorithms that avoid such situations. A *non-blocking algorithm* avoids any kind of locking, i.e., no blocked thread can block another thread. A *lock-free algorithm* moreover guarantees that some thread in the system can always make progress towards reaching its overall goal. Finally, a *wait-free algorithm* guarantees progress by each thread. For more details and examples refer to a widely used textbook [234].

#### Open Problem 7 (Scalable concurrent algorithms with or without locks)

Many lock-free algorithms seem to be so complicated that papers on them only discuss their correctness. However, we also would like to know their scalability when running on p PEs (i.e., hardware threads). There are very few results in

this direction and solving such problems might be an important step to better concurrent algorithms. In particular, many current lock-free algorithms have severe scalability bottlenecks. An example on priority queues can be found in Section 12.5.2.<sup>11</sup> If we use an asynchronous PRAM model, we can also exploit assumptions that do not hold for general lock-free algorithms. In particular, each thread t gets permanently assigned a PE. Thus, we can often *prove* that t will only hold a lock for a constant amount of time. Therefore, locking does not necessarily stand in the way of progress guarantees.<sup>12</sup>

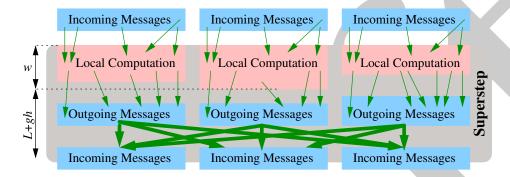

## 2.4.5 The Work-Span Model

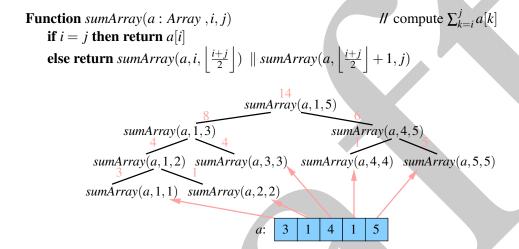

A more abstract way to look at shared-memory computations is the *work-span model* (aka *work-depth model*) where we abstract from the actual number of processors [4,75]. We only look (1): at the total *work W* performed by a computation, i.e., the time needed for machine operations that are part of the actual computation, and (2): at its *span T* $_{\infty}$ (aka *depth*), i.e., the longest sequence of dependent operations within the computation. Roughly, the span is the time needed when an infinite number of processors is available. The computation forms a graph of dependencies that is unfolded using *fork operations* that spawn additional threads and atomic shared-memory operations. The model comes in different variants depending on what exactly these operations can do. In this book, the default will be binary forking [75] together with the aCRQW model from Section 2.4.2 and the atomic operations from Section 2.4.3. In particular, this allows parallel recursion. Figure 2.13 gives an example. Circuit models (see Section 2.8) take a similar, more low-level and hardware-oriented view of computations.

**Exercise 12** Show that function sumArray in Figure 2.13 has work O(n) and span  $O(\log n)$ . Implement it using a system supporting task creation. Now tune it, e.g. by using a larger base case.

An obvious lower bound for the time needed to execute a computation in the work-span model on a PRAM with p PEs is

$$T(p) = \frac{W}{p} + T_{\infty}.$$

<sup>&</sup>lt;sup>11</sup>The underlying paper [482] also gives a curious example of an algorithm that uses locks but is nevertheless wait-free because it never waits for a lock.

<sup>&</sup>lt;sup>12</sup>In practice, we may have to ensure that the operating system indeed never takes away the assigned hardware thread, e.g., by reserving one or several cores for the operating system. We also have to be careful about threads that perform I/Os.

Figure 2.13: A function using parallel recursion to compute the sum of the elements of an array. The picture gives an example for the array [3,1,4,1,5].

A crucial result is that using appropriate load balancers, this is also an upper bound at least in a probabilistic sense using randomization in a work-stealing load balancer [78] (see also [412, Section 14.5, 14.6]).

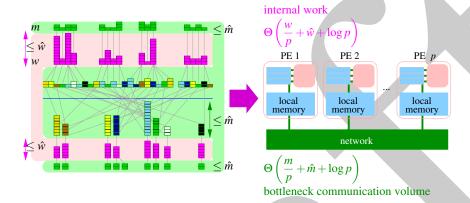

# 2.4.6 Parallel Memory Hierarchies

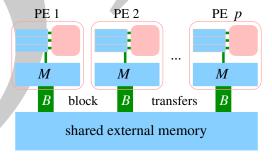

The Parallel External Memory (PEM) model [26] is a natural extension of PRAMs. RAMs with fast memory of size M each are attached to a large shared memory. As

Figure 2.14: The parallel external memory model (PEM).

in the I/O model, access to that memory is in blocks of size *B*. As with PRAMs, we can consider several variants with respect to what kind of concurrent accesses are supported. PEM is an elegant way to model the differences between the cost of local and global memory accesses.

**Exercise 13** Describe an algorithm that transposes an  $n \times n$  matrix on a PEM using  $O(n^2/Bp)$  I/O steps assuming  $M > B^2$ .

However, as with basic PRAMs, the PEM model is unrealistic with respect to the cost of synchronization and contention. To handle this issue, let us introduce an asynchronous variant with queued writing,  $PEM^+$ , that adds block access to the aCRQW PRAM model from Section 2.4.2. One can now also consider atomic operations on the block level. Unfortunately, current processor architectures only support atomic operations on machine words (and sometimes on double words). On the other hand, hardware transactional memory (see also Section 2.4.3) operates on cache lines. Hence, let us assume that PEM<sup>+</sup> also supports transactions.

One issue with the PEM model that has led to confusion is that Vitter and Shriver [469] had previously introduced a parallel external memory model. But for them, M is the *overall* size of the fast memory. This implies that the bounds based on the original model [469] (e.g., [388]) are harder to obtain than bounds in the PEM model and require more sophisticated algorithms that treat communication and I/Os separately.

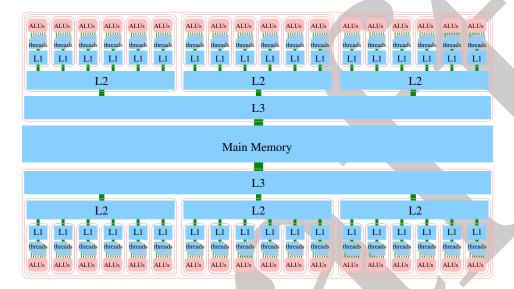

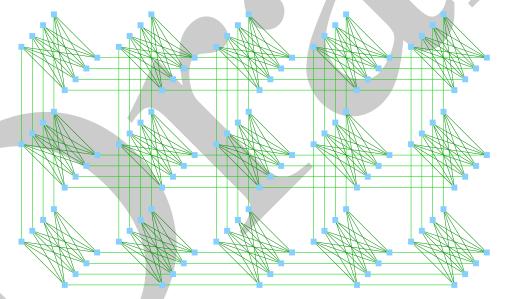

The PEM model is a good abstraction of a shared-memory machine where the PEs have a private cache and symmetric access to the main memory. However, many practical machines have a more complicated hierarchical structure that can be approximated by a tree of PEs. Level i of the memory is partitioned into  $k_i$  pieces and a subtree of  $p/k_i$  PEs share access to that piece. Consider a fictitious but realistic example: Four hardware threads of a core may share an L1 cache. Six cores on a *chiplet* may share an L2 cache. Three chiplets may share an L3 cache on a processor *socket*. Two sockets may have shared access to the main memory. Figure 2.15 illustrates this example. Some of the aspects shown in Figure 2.1 can also be mapped to this model. In that example,  $k_1 = k_2$ , i.e., each core has its own L1 and L2 cache. This can make sense in practice since these two cache levels can reflect different tradeoffs between latency, size, and cost per bit. Similarly, SSDs and main memory may both be attached to sockets although they differ in size, cost, latency, and volatility.

Section 2.5.5 further generalizes the hierarchical model to allow horizontal communication on each level. In practice, this is also relevant in a shared-memory

Figure 2.15: Example of a shared-memory machine with p = 144 threads,  $k_1 = 36$  cores,  $k_2 = 6$  chiplets, and  $k_3 = 2$  sockets.

setting. In particular, each socket may be directly connected to several main memory modules. Every core can still access every memory module also on remote sockets. However, the access costs will be larger the "farther away" the memory module is. This issue is known as *non-uniform memory access (NUMA)*. Sockets<sup>13</sup> are therefore also called *NUMA nodes*.

Of course, completely analyzing algorithms in such a complex model is even more forbidding than multilevel external memory. However, we can adopt the approach to analyze a selected aspect like the number of I/Os on a particular level that experiments may indicate as a bottleneck. We can also generalize the approach of cache-oblivious algorithms to parallel memory hierarchies [118].

#### 2.4.7 Graphics Processing Units (GPUs), Accelerators, etc.

The transition of traditional general-purpose sequential processors to multi-core processors has been a fairly conservative process leading to processors supporting a moderate number of parallel threads, favoring fast individual cores with

<sup>&</sup>lt;sup>13</sup>Or any part of a machine that has uniform access to a set of memory modules, e.g., a chiplet within a multi-chip module.

large cache memories and large main memories. It turned out that this is not the ideal path to maximum peak arithmetic performance or maximum memory bandwidth. A more radical approach is to support massive parallelism even on a single chip dedicating a larger fraction of chip area to arithmetic units and to connect it to memory chips with a different tradeoff between bandwidth, latency, and cost. Figure 2.16 illustrates this tradeoff. Originally fueled by the large market for hardware accelerated computer graphics (e.g., for games), so-called *graphics processing units* (*GPUs*) have been particularly successful. Since the beginning of the millennium, they developed from special purpose processors to general purpose processors (*GPGPUs*) that are less and less different from traditional CPUs. GPU applications are now coming from a much wider range, with machine learning and mining crypto-currencies as major driving forces. In high-performance computing, the biggest machines currently invest heavily in GPU hardware and thus exert major pressure on application developers to use GPUs for more and more applications.